- 您现在的位置:买卖IC网 > Sheet目录3851 > PIC32MX130F064D-I/ML (Microchip Technology)IC MCU 32BIT 64KB FLASH 44-QFN

2011-2012 Microchip Technology Inc.

Preliminary

DS61168D-page 1

PIC32MX1XX/2XX

Operating Conditions

2.3V to 3.6V, -40C to +105C, DC to 40 MHz

Core: 40 MHz MIPS32 M4K

MIPS16e mode for up to 40% smaller code size

1.56 DMIPS/MHz (Dhrystone 2.1) performance

Code-efficient (C and Assembly) architecture

Single-cycle (MAC) 32x16 and two-cycle 32x32 multiply

Clock Management

0.9% internal oscillator

Programmable PLLs and oscillator clock sources

Fail-Safe Clock Monitor (FSCM)

Independent Watchdog Timer

Fast wake-up and start-up

Power Management

Low-power management modes (Sleep, Idle)

Integrated Power-on Reset and Brown-out Reset

0.5 mA/MHz dynamic current (typical)

20 μA IPD current (typical)

Audio Interface Features

Data communication: I2S, LJ, RJ, DSP modes

Control interface: SPI and I2C

Master clock:

- Generation of fractional clock frequencies

- Can be synchronized with USB clock

- Can be tuned in run-time

Advanced Analog Features

ADC Module:

- 10-bit 1.1 Msps rate with one S&H

- Up to 10 analog inputs on 28-pin devices and 13

analog inputs on 44-pin devices

Flexible and independent ADC trigger sources

Charge Time Measurement Unit (CTMU):

- Supports mTouch capacitive touch sensing

- Provides high-resolution time measurement (1 ns)

- On-chip temperature measurement capability

Comparators:

- Up to three Analog Comparator modules

- Programmable references with 32 voltage points

Timers/Output Compare/Input Capture

Five General Purpose Timers:

- Five 16-bit and up to two 32-bit Timers/Counters

Five Output Compare (OC) modules

Five Input Capture (IC) modules

Peripheral Pin Select (PPS) to allow function remap

Real-Time Clock and Calendar (RTCC) module

Communication Interfaces

USB 2.0-compliant Full-speed OTG controller

Two UART modules (10 Mbps)

- Supports LIN 2.0 protocols and IrDA support

Two 4-wire SPI modules (20 Mbps)

Two I2C modules (up to 1 Mbaud) with SMBus support

Peripheral Pin Select (PPS) to allow function remap

Parallel Master Port (PMP)

Direct Memory Access (DMA)

Four channels of hardware DMA with automatic data

size detection

Two additional channels dedicated for USB

Programmable Cyclic Redundancy Check (CRC)

Input/Output

15 mA source/sink on all I/O pins

5V-tolerant pins

Selectable open drain, pull-ups, and pull-downs

External interrupts on all I/O pins

Qualification and Class B Support

AEC-Q100 REVG (Grade 2 -40C to +105C) planned

Class B Safety Library, IEC 60730

Debugger Development Support

In-circuit and in-application programming

4-wire MIPS Enhanced JTAG interface

Unlimited program and six complex data breakpoints

IEEE 1149.2-compatible (JTAG) boundary scan

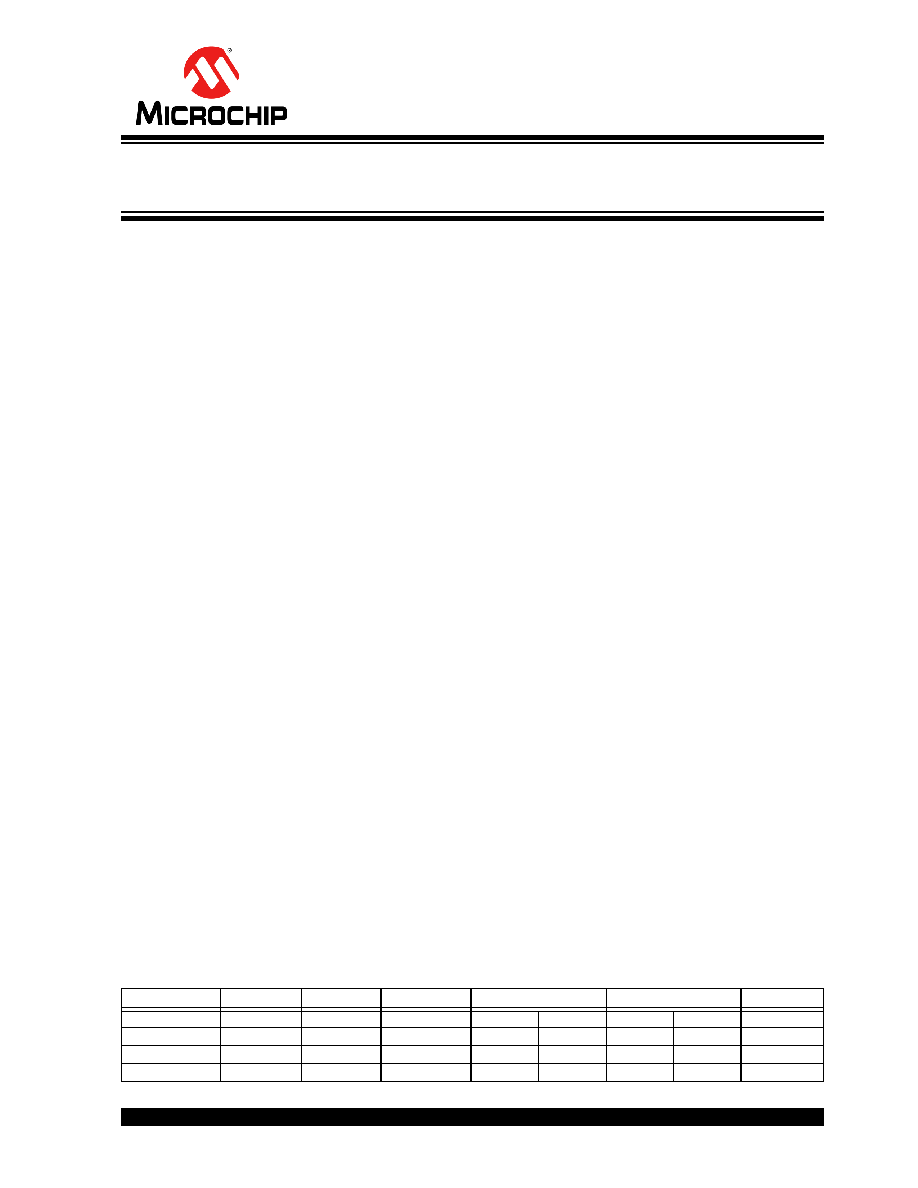

Packages

Type

SOIC

SSOP

SPDIP

QFN

VTLA

TQFP

Pin Count

28

44

36

44

I/O Pins (up to)

21

34

25

34

Contact/Lead Pitch

1.27

0.65

0.100''

0.65

0.50

0.80

Dimensions

17.90x7.50x2.65

10.2x5.3x2

1.365x.285x.135''

6x6x0.9

8x8x0.9

5x5x0.9

6x6x0.9

10x10x1

Note: All dimensions are in millimeters (mm) unless specified.

32-bit Microcontrollers (up to 128 KB Flash and 32 KB SRAM) with

Audio and Graphics Interfaces, USB, and Advanced Analog

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC18LF46K80-I/ML

MCU PIC ECAN 64KB FLASH 44QFN

AT89S51-24JI

IC 8051 MCU 4K FLASH 44PLCC

AT89S51-24JC

IC 8051 MCU 4K FLASH 44PLCC

AT89S51-24AI

IC 8051 MCU 4K FLASH 44TQFP

AT89S51-24AC

IC 8051 MCU 4K FLASH 44 TQFP

AT89LS52-16PI

IC 8051 MCU FLASH 8K 40DIP

AT89LS52-16PC

IC MCU 8K FLASH LV 16MHZ 40-DIP

AT89LS52-16JI

IC 8051 MCU FLASH 8K 44PLCC

相关代理商/技术参数

PIC32MX130F064D-I/PT

功能描述:32位微控制器 - MCU 32B MCU 64KB FL 16KB RAM 40MHz 44Pin

RoHS:否 制造商:Texas Instruments 核心:C28x 处理器系列:TMS320F28x 数据总线宽度:32 bit 最大时钟频率:90 MHz 程序存储器大小:64 KB 数据 RAM 大小:26 KB 片上 ADC:Yes 工作电源电压:2.97 V to 3.63 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:LQFP-80 安装风格:SMD/SMT

PIC32MX130F064D-I/TL

功能描述:32位微控制器 - MCU 32B MCU 64KB FL 16KB RAM 40MHz 44Pin

RoHS:否 制造商:Texas Instruments 核心:C28x 处理器系列:TMS320F28x 数据总线宽度:32 bit 最大时钟频率:90 MHz 程序存储器大小:64 KB 数据 RAM 大小:26 KB 片上 ADC:Yes 工作电源电压:2.97 V to 3.63 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:LQFP-80 安装风格:SMD/SMT

PIC32MX130F064DT-I/ML

功能描述:32位微控制器 - MCU 32B MCU 64KB FL 16KB RAM 40MHz 44Pin

RoHS:否 制造商:Texas Instruments 核心:C28x 处理器系列:TMS320F28x 数据总线宽度:32 bit 最大时钟频率:90 MHz 程序存储器大小:64 KB 数据 RAM 大小:26 KB 片上 ADC:Yes 工作电源电压:2.97 V to 3.63 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:LQFP-80 安装风格:SMD/SMT

PIC32MX130F064DT-I/PT

功能描述:32位微控制器 - MCU 32B MCU 64KB FL 16KB RAM 40MHz 44Pin

RoHS:否 制造商:Texas Instruments 核心:C28x 处理器系列:TMS320F28x 数据总线宽度:32 bit 最大时钟频率:90 MHz 程序存储器大小:64 KB 数据 RAM 大小:26 KB 片上 ADC:Yes 工作电源电压:2.97 V to 3.63 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:LQFP-80 安装风格:SMD/SMT

PIC32MX130F064DT-I/TL

功能描述:32位微控制器 - MCU 32B MCU 64KB FL 16KB RAM 40MHz 44Pin

RoHS:否 制造商:Texas Instruments 核心:C28x 处理器系列:TMS320F28x 数据总线宽度:32 bit 最大时钟频率:90 MHz 程序存储器大小:64 KB 数据 RAM 大小:26 KB 片上 ADC:Yes 工作电源电压:2.97 V to 3.63 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:LQFP-80 安装风格:SMD/SMT

PIC32MX130F064DT-V/ML

功能描述:32位微控制器 - MCU 32B MCU 64KB FL 16KB RAM 40MHz 44Pin

RoHS:否 制造商:Texas Instruments 核心:C28x 处理器系列:TMS320F28x 数据总线宽度:32 bit 最大时钟频率:90 MHz 程序存储器大小:64 KB 数据 RAM 大小:26 KB 片上 ADC:Yes 工作电源电压:2.97 V to 3.63 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:LQFP-80 安装风格:SMD/SMT

PIC32MX130F064DT-V/PT

功能描述:32位微控制器 - MCU 32B MCU 64KB FL 16KB RAM 40MHz 44Pin

RoHS:否 制造商:Texas Instruments 核心:C28x 处理器系列:TMS320F28x 数据总线宽度:32 bit 最大时钟频率:90 MHz 程序存储器大小:64 KB 数据 RAM 大小:26 KB 片上 ADC:Yes 工作电源电压:2.97 V to 3.63 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:LQFP-80 安装风格:SMD/SMT

PIC32MX130F064DT-V/TL

功能描述:32位微控制器 - MCU 32B MCU 64KB FL 16KB RAM 40MHz 44Pin

RoHS:否 制造商:Texas Instruments 核心:C28x 处理器系列:TMS320F28x 数据总线宽度:32 bit 最大时钟频率:90 MHz 程序存储器大小:64 KB 数据 RAM 大小:26 KB 片上 ADC:Yes 工作电源电压:2.97 V to 3.63 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:LQFP-80 安装风格:SMD/SMT